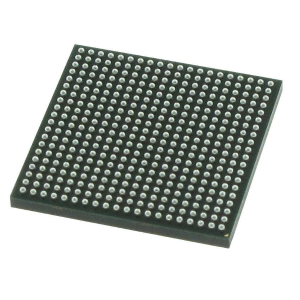

LCMXO1200C-3TN144I FPGA – Forritanleg hliðarfylki 1200 LUT 113 IO 1,8 /2,5/3,3V -3 hraða I

♠ Vörulýsing

| Vörueiginleiki | Eiginleikagildi |

| Framleiðandi: | Ristargrind |

| Vöruflokkur: | FPGA - Forritanleg hliðarfylki á vettvangi |

| RoHS: | Nánari upplýsingar |

| Röð: | LCMXO1200C |

| Fjöldi rökfræðiþátta: | 1200 LE |

| Fjöldi inn-/útganga: | 113 Inntak/Úttak |

| Spenna - Lágmark: | 1,71 V |

| Spenna - Hámark: | 3,465 V |

| Lágmarks rekstrarhitastig: | - 40°C |

| Hámarks rekstrarhitastig: | + 100°C |

| Gagnahraði: | - |

| Fjöldi senditæki: | - |

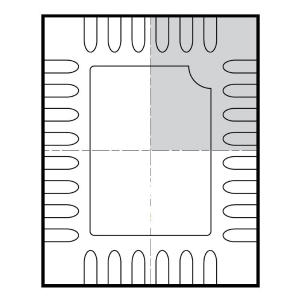

| Festingarstíll: | SMD/SMT |

| Pakki/Kassi: | TQFP-144 |

| Umbúðir: | Bakki |

| Vörumerki: | Ristargrind |

| Dreift vinnsluminni: | 6,4 kbit |

| Innbyggt blokkvinnsluminni - EBR: | 9,2 kbit |

| Hæð: | 1,4 mm |

| Lengd: | 20 mm |

| Hámarks rekstrartíðni: | 500 MHz |

| Rakaviðkvæmt: | Já |

| Fjöldi rökfræðiblokka - LABs: | 150 rannsóknarstofur |

| Rekstrarstraumur: | 21 mA |

| Rekstrarspenna: | 1,8 V/2,5 V/3,3 V |

| Tegund vöru: | FPGA - Forritanleg hliðarfylki á vettvangi |

| Magn verksmiðjupakkningar: | 60 |

| Undirflokkur: | Forritanleg rökfræði-IC |

| Heildarminni: | 15,6 kbit |

| Breidd: | 20 mm |

| Þyngd einingar: | 1,319 grömm |

Óstöðugt, óendanlega endurstillanlegt

• Kveikir strax – kviknar á örsekúndum

• Ein flís, engin þörf á utanaðkomandi stillingarminni

• Frábær hönnunaröryggi, enginn bitastraumur til að hlera

• Endurstilla SRAM-byggða rökfræði á millisekúndum

• SRAM og stöðugt minni forritanlegt í gegnum JTAG tengi

• Styður bakgrunnsforritun á óstöðugu minni

Svefnhamur

• Leyfir allt að 100-falda minnkun á stöðustraumi

TransFR™ endurstilling (TFR)

• Uppfærsla á rökfræði á vettvangi á meðan kerfið er í gangi

Hár I/O til rökfræðiþéttleiki

• 256 til 2280 LUT4

• 73 til 271 inntak/úttak með fjölbreyttum pakkavalkostum

• Þéttleikaflutningur studdur

• Blýfríar/RoHS-samræmir umbúðir

Innbyggt og dreift minni

• Allt að 27,6 Kbita sysMEM™ innbyggt blokkvinnsluminni

• Allt að 7,7 Kbit dreift vinnsluminni

• Sérstök FIFO stjórnunarrökfræði

Sveigjanlegur I/O biðminni

• Forritanlegt sysIO™ biðminni styður fjölbreytt úrval af viðmótum:

– LVCMOS 3.3/2.5/1.8/1.5/1.2

– LVTTL

– PCI

– LVDS, Bus-LVDS, LVPECL, RSDS

sysCLOCK™ PLL-einingar

• Allt að tvær hliðrænar PLL-einingar á tæki

• Margföldun, deiling og fasabreyting klukku

Stuðningur á kerfisstigi

• IEEE staðall 1149.1 mörkaskönnun

• Innbyggður sveiflari

• Tæki virka með 3,3V, 2,5V, 1,8V eða 1,2V aflgjafa

• IEEE 1532 samhæfð forritun í kerfinu